|

itpp_sci

1.0.0

it++ based simulation framework for scicoslab, scilab and scipy

|

|

itpp_sci

1.0.0

it++ based simulation framework for scicoslab, scilab and scipy

|

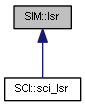

linear shift register

Core function: SIM::lsr.process()

More...

Public Member Functions | |

| lsr () | |

| ~lsr () | |

| void | set_length (int L) |

| void | set_symbol_size (int W) |

| void | set_reset_state (const bvec &binit) |

| void | set_output (const bvec &yout) |

| void | set_state (const bvec &state) |

| bvec | get_state (void) |

| bvec | get_reset_state () |

| bvec | get_output () |

| int | get_length (void) |

| int | get_symbol_size () |

| bmat | process (const bvec &ce, const bmat &x) |

linear shift register

Core function: SIM::lsr.process()

linear shift register with clocked interface as used in BERT

Shift register (aka memory) is a bvec with size of L bits

Input is reprsented by bmat[N,W] for N ce[] ticks

For i-th tick one row in x bmat represents one symbol with W bits

x[i,:] = [x0(0), x0(1),...x0(W-1)]

For active tick ce[i] Input symbol is shifted in memory as W - LSB bits (from index 0)

mem(i) = [x[0:W-1] | mem[0:L-W-1]]

output is bvec with W bit shifted out

y[i,:] = m[L-W:L-1]

|

inline |

|

inline |

| int SIM::lsr::get_length | ( | void | ) |

get length of shift register

| bvec SIM::lsr::get_output | ( | void | ) |

get initial/idle output vector

| bvec SIM::lsr::get_reset_state | ( | ) |

get reset binary vector

| bvec SIM::lsr::get_state | ( | void | ) |

get state of shift register (aka memory)

| int SIM::lsr::get_symbol_size | ( | void | ) |

get size of input/output symbol

| bmat SIM::lsr::process | ( | const bvec & | ce, |

| const bmat & | x | ||

| ) |

for active clock ticks ce[i]

right shift in one input symbol x[i,:] and shift out one symbol y[i,:]

| ce | - [bvec] - clock enable vector - sizeof(ce)=N |

| x | - [bmat] - input symbols matrix - sizeof(x)=[N,W] |

| void SIM::lsr::set_length | ( | int | L | ) |

set lenght of shift register

| [in] | L | - [int] size of shift register (aka memory) |

| void SIM::lsr::set_output | ( | const bvec & | yout | ) |

sets initial/idle output vector

| [in] | yout | - [bvec] y0 = yout |

| void SIM::lsr::set_reset_state | ( | const bvec & | binit | ) |

set reset vector

| [in] | binit | - [bvec] reset vector |

| void SIM::lsr::set_state | ( | const bvec & | state | ) |

set state of shift (aka memory) register

| [in] | state | - [bvec] vector to set |

| void SIM::lsr::set_symbol_size | ( | int | W | ) |

set size of a symbol

| [in] | W | - [int] size of a symbol |

1.8.9.1

1.8.9.1