complex circular buffer

Core functions SIM::circbuff_x.process() SIM::circbuff_x.generate()

More...

complex circular buffer

Core functions SIM::circbuff_x.process() SIM::circbuff_x.generate()

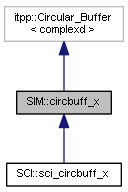

itpp::circular_buffer<complex> derived class with clocked interface

| SIM::circbuff_x::circbuff_x |

( |

| ) |

|

|

inline |

| SIM::circbuff_x::~circbuff_x |

( |

| ) |

|

|

inline |

| cvec SIM::circbuff_x::generate |

( |

const bvec & |

ce | ) |

|

for active clock ticks [ce] fetch sample and and put back into the buffer

if (ce) {yout = get(); put(yout);

- Parameters

-

| ce | - [bvec] clock_enable vector |

- Returns

- y - [cvec]

| complex< double > SIM::circbuff_x::get_output |

( |

void |

| ) |

|

get output value

- Returns

- - [double] y0

| int SIM::circbuff_x::get_size |

( |

void |

| ) |

|

get buffer size

- Returns

- - [int] buffer size

| cvec SIM::circbuff_x::process |

( |

const bmat & |

ceio, |

|

|

const cvec & |

x |

|

) |

| |

for active input clock ticks [cei] put input samples [x]

if (cei[i]) { put(x[i]) }

for active output clock ticks [ceo] update y by fetching one sample

if (ceo[i]) { yout = get() }

- Parameters

-

| ceio | - [bmat][cei|ceo] input/output clock_enable vector |

| x | - [cvec] - input samples |

- Returns

- y - [cvec] - output samples

| void SIM::circbuff_x::set_output |

( |

complexd |

yout | ) |

|

set output value y0

- Parameters

-

| void SIM::circbuff_x::set_size |

( |

int |

m | ) |

|

set buffer size

- Parameters

-

The documentation for this class was generated from the following files:

- C:/jobs/vcc/itpp_sci/include/sim/sim_circbuff_x.hpp

- C:/jobs/vcc/itpp_sci/sim_lib/code/sim_circbuff_x.cpp

1.8.9.1

1.8.9.1